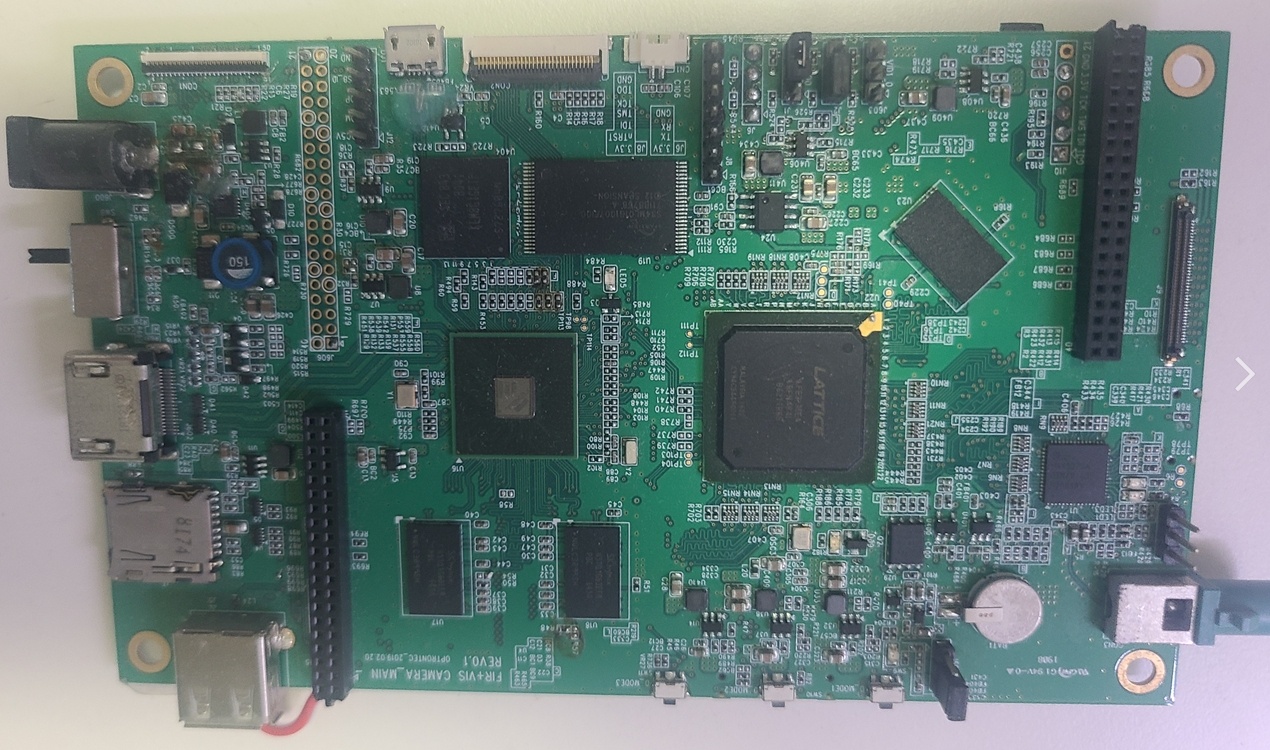

Multi Camera 영상 합성·레코딩 시스템 (FPGA + AP)

멀티 카메라 영상을 FPGA에서 합성(프레임 동기화/스케일링/LDC)하고, AP에서 레코딩 및 RTSP 서버로 스트리밍하는 임베디드 시스템

프로젝트 개요

본 프로젝트는 다수의 카메라 입력을 FPGA에서 프레임 동기화 및 영상 보정/합성을 수행한 뒤, AP에서 프레임 버퍼링, 영상 레코딩, RTSP 스트리밍 서버 기능을 제공하는 멀티 카메라 임베디드 시스템을 구축한 프로젝트입니다.

고객사

Optrontec

역할 (개발 범위)

- 보드 설계 및 제작(시제품 개발 포함)

- FPGA 기반 영상 합성 파이프라인 구현 및 검증 환경 구축

- AP 임베디드 환경 구성(Yocto) 및 카메라/레코딩/스트리밍 기능 개발

- 고객 요구사항 반영 및 기능 고도화 지원

핵심 기능

- FPGA : 멀티 카메라 입력(MIPI Rx) 프레임 동기화(Frame Sync) 및 스케일링(Scaler)

- FPGA : LDC 기반 영상 피팅(Fitting) 및 영상 합성(Merge)

- AP : 카메라 드라이버 및 프레임 버퍼 처리

- AP : 영상 레코딩 기능 및 RTSP 스트리밍 서버 제공

사용 플랫폼 / 기술

주안점

- 하드웨어(보드/전원/신호) 안정성 확보 및 장시간 운용 고려

- FPGA 시뮬레이션/검증 환경 구축을 통한 기능 신뢰성 확보

- AP 임베디드 개발 환경(Yocto) 신속 구축 및 고객 요청사항의 빠른 반영

* 상세 RTL/합성 파라미터 및 산출물은 NDA 및 협의 범위 내에서 공유 가능합니다.

프로젝트 문의 포인트 이미지

포인트 이미지